3.6 双口RAM和多模块存储器

3.6 双口RAM和多模块存储器 CPU和主存储器的速度不匹配问题一直以来都是计算机系统发展的障碍,到现在,这个

3.6 双口RAM和多模块存储器

CPU和主存储器的速度不匹配问题一直以来都是计算机系统发展的障碍,到现在,这个问题变得越来越严重,以至于主存的存储速度成为了计算机系统的瓶颈。为了解决这一瓶颈,尝试了多种办法,除通过寻找高速元件来提高访问速度外,还可以通过采用双口RAM和多模块存储器,使在一个存取周期内可以并行地读写多个字,从而提高存储器的访问速度。

1.双口RAM

双口RAM是因同一个RAM具有两组相对独立的读写控制线路而得名,它可以进行并行的独立操作。可以说双口RAM是具有两个独立端口的存储器,而每个端口又具有各自的地址线、数据线和控制线,可以对存储器中任何位置上的数据进行独立的存取操作。

双口RAM是常见的共享式多端口存储器,其最大的特点是存储数据共享。它允许两个独立的CPU或控制器同时异步访问存储单元。既然数据共享,就必须存在访问仲裁控制,否则就会出现错误或冲突。两个端口对同一内存操作有4种情况:

① 两个端口不同时对同一地址单元存取数据;

② 两个端口同时对同一地址单元读出数据;

③ 两个端口同时对同一地址单元写入数据;

④ 两个端口同时对同一地址单元,一个写入数据,另一个读出数据。

在第①、第②种情况时,两个端口的存取不会出现错误,第③种情况会出现写入错误,第④种情况会出现读出错误。为避免第③、第④种错误情况的出现,双口RAM设计有硬件“ ”功能输出,其工作原理如下。

”功能输出,其工作原理如下。

当左、右端口不对同一地址单元存取时, 可正常存取;当左、右端口对同一地址单元存取时,有一个端口的

可正常存取;当左、右端口对同一地址单元存取时,有一个端口的 禁止数据的存取。此时,两个端口中,哪个存取请求信号出现在前,则其对应的

禁止数据的存取。此时,两个端口中,哪个存取请求信号出现在前,则其对应的 允许存取;哪个存取请求信号出现在后,则其对应的

允许存取;哪个存取请求信号出现在后,则其对应的 禁止其写入数据。需要注意的是,两端口间的存取请求信号出现时间要相差在5ns以上,否则仲裁逻辑无法判定哪一个端口的存取请求信号在前;在无法判定哪个端口先出现存取请求信号时,控制线

禁止其写入数据。需要注意的是,两端口间的存取请求信号出现时间要相差在5ns以上,否则仲裁逻辑无法判定哪一个端口的存取请求信号在前;在无法判定哪个端口先出现存取请求信号时,控制线 和

和 只有一个为低电平,不会同时为低电平。这样,就能保证对应于

只有一个为低电平,不会同时为低电平。这样,就能保证对应于 的端口能进行正常存取,对应于

的端口能进行正常存取,对应于 的端口不存取,从而避免双端口存取出现错误。

的端口不存取,从而避免双端口存取出现错误。

2.多模块存储器

顾名思义,多模块存储器是指由多个模块组成的存储器,不过这些模块具有相同的容量和存取速度,各模块都有独立的地址寄存器、数据寄存器、地址译码、驱动电路和读/写电路,它们既能并行工作,又能交叉工作。

多模块存储器一般采用线性编制方式。对地址在各模块中有两种安排方式,分别是顺序方式和交叉方式。假设一个存储器容量为16个字,分成M0~M3这4个模块。

在顺序方式中,访问地址是按一个个模块顺序分配的,即先将1到4顺序分配给M0模块的4个字,然后再接着给模块M1的4个字分配访问地址5到8,以此类推完成地址分配。这样,存储16个字可由4位地址寄存器指示,高2位用于选择模块,低2位用于选择模块中的字,这样连续的地址分配在同一模块内。因此,在对顺序存储方式中某模块进行存取操作时,其他模块不工作,当该模块出现故障时,其他模块也能正常工作。使用这种方式易于扩充存储器容量,其缺点是各模块间只能进行串行工作,限制了存储器的带宽。

在交叉方式中,如果将16个字分成4个模块,其地址分配方案不同,它先将4个线性地址(0、1、2、3)依次分配给M0~M3,再将线性地址(4、5、6、7)依次分配给M0~M3,以此类推完成地址分配。这样,存储16个字也可由4位地址寄存器指示,不过其高2位用于选择模块中的字,而低2位用于选择模块,由此可见连续的地址分配在相邻的不同模块内,而同一模块内的地址是不连续的。因此,对连续字的成块传送,交叉方式的存储器可以实现多模块流水式并行存取,提高了存储器的带宽,从而提高了存储器的存取速度。

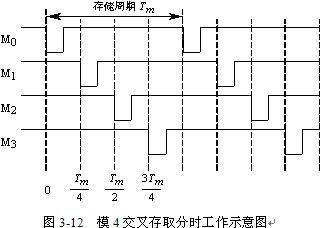

采用多模块交叉方式的存储器称为多模块交叉存储器。这种存储器采用分时启动的方法,可以在不改变每个模块存取周期的前提下,提高整个主存的速度。在第一个存储周期的开始时刻启动模块M0,在 时刻分别启动模块M1、M2、M3,如图3-12所示示意了模4交叉存取的时间关系。

时刻分别启动模块M1、M2、M3,如图3-12所示示意了模4交叉存取的时间关系。

在4个模块完全并行的理想情况下,整个主存的有效周期缩小到原来模块存取周期的 ,数据传送的平均速度提高到原来的4倍。但是,在实际应用中,当出现数据相关和程序转移时,将破坏并行性,不可能达到上述理想值,但比顺序方式还是提高了不少。

,数据传送的平均速度提高到原来的4倍。但是,在实际应用中,当出现数据相关和程序转移时,将破坏并行性,不可能达到上述理想值,但比顺序方式还是提高了不少。

关于"最后阶段,真题的正确打开方式_备考经验_考研帮"有15名研友在考研帮APP发表了观点

扫我下载考研帮

最新资料下载

- 2024-03-15考研资料免费分享,公共课专业课都有,23最新的

- 2024-03-1125考研公共课免费分享

- 2024-03-06mpa复试

- 2024-03-0624新传考研资料 适用多种院校

- 2024-03-0624、25考研公共课免费分享

- 2024-03-05831程序设计语言

- 2024-03-05求资料

2021考研热门话题进入论坛

- 2022-01-24【入版必看】2021考研全程备考规划!

- 2021-12-16424分上岸!21级成都大学广播电视第1名三跨二战上岸经

- 2021-01-20学长学姐帮2020还没对你说的话,今天这就告诉你

- 2024-02-21西南交通大学土木考研

- 2024-01-31华中师范语言所考研资料

- 2024-01-31华中师范大学语言所考研资料

- 2024-01-27武汉大学法学学硕考研经验贴

考研帮地方站更多

你可能会关心:

来考研帮提升效率