2.4 术逻辑单元

2.4 算术逻辑单元 算术逻辑单元是运算器的主要部件,而运算器是对信息进行处理和运算的单元。经常需要进行

2.4 算术逻辑单元

算术逻辑单元是运算器的主要部件,而运算器是对信息进行处理和运算的单元。经常需要进行的运算有算术运算和逻辑运算等。

2.4.1 串行加法器和并行加法器

加法器是算术逻辑单元的重要组成部分,它是一种用于加法运算的器件,其本身主要由全加器再配以其他必要的逻辑电路组成,根据组成加法器的全加器个数,可以将加法器分为串行加法器和并行加法器。

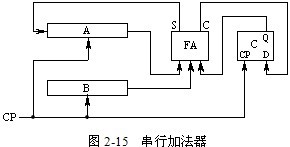

1.串行加法器

在串行加法器中,只有一个全加器,数据逐位串行送入加法器进行运算,如图2-15所示。图中FA是全加器,A、B是两个具有右移功能的寄存器,C为进位触发器。由移位寄存器从低位到高位逐位串行提供操作数相加。如果操作数长n位,加法就要分n次进行,每次产生一位和,并串行地送回A寄存器。进位触发器用来寄存进位信号,以便参与下一次的运算。

串行加法器具有器件少、成本低的优点,但运算速度太慢,所以除去某些低速的专用运算器外很少采用。

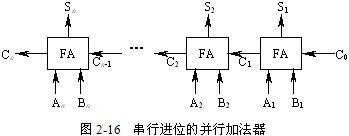

2.并行加法器

并行加法器由多个全加器组成,其全加器个数的多少取决于机器的字长,由于并行加法器可同时对数据的各位相加,读者可能会认为数据的各位能同时运算,其实并不是这样的。这是因为虽然操作数的各位是同时提供的,但低位运算所产生的进位会影响高位的运算结果。例如:11…11和00…01相加,最低位产生的进位将逐位影响至最高位,因此,并行加法器需要一个最长运算时间,它主要是由进位信号的传递时间决定的,而每个全加器本身的求和延迟只是次要因素。很明显,提高并行加法器速度的关键是尽量加快进位产生和传递的速度。

并行加法器中的每一个全加器都有一个从低位送来的进位输入和一个传送给高位的进位输出。通常将传递进位信号的逻辑线路连接起来构成的进位网络称为进位链。每一位的进位表达式为:

Ci=AiBi+(Ai⊕Bi)Ci-1

其中,“AiBi”取决于本位参加运算的两个数,而与低位进位无关,因此称AiBi为进位产生函数(本次进位产生),用Gi表示,其含义是:若本位的两个输入均为1,必然要向高位产生进位。“(Ai⊕Bi)Ci-1”则不但与本位的两个数有关,还依赖于低位送来的进位,因此称Ai⊕Bi为进位传递函数(低位进位传递),用Pi表示,其含义是:当两个输入中有一个为1,低位传来的进位Ci-1将向更高位传送,所以进位表达式又可以写成:

Ci=Gi+PiCi-1

把n个全加器串接起来,就可进行两个n位数的相加。这种加法器称为串行进位的并行加法器,如图2-16所示。串行进位又称行波进位,每一级进位直接依赖于前一级的进位,即进位信号是逐级形成的。

其中:C1=G1+P1C0

C2=G2+P2C1

…

Cn=Gn+PnCn-1

串行进位的并行加法器的总延迟时间与字长成正比,字长越长,总延迟时间就越长。假设将一级与门、或门的延迟时间定为ty,从上述公式中可以看出,每一级全加器的进位延迟时间为2ty。在字长为n位的情况下,若不考虑Gi、Pi的形成时间,从C0→Cn的最长延迟时间为2nty(设C0为加法器最低位的进位输入,Cn为加法器最高位的进位输出)。

显然,串行进位方式的进位延迟时间太长了,要提高加法运算的速度,就要尽可能地减少进位延迟时间,也就是要改进进位方式,这就产生了并行进位方式和分组并行进位方式。限于篇幅,本书不详细介绍这两种方式的具体内容。

关于"最后阶段,真题的正确打开方式_备考经验_考研帮"有15名研友在考研帮APP发表了观点

扫我下载考研帮

最新资料下载

- 2024-03-15考研资料免费分享,公共课专业课都有,23最新的

- 2024-03-1125考研公共课免费分享

- 2024-03-06mpa复试

- 2024-03-0624新传考研资料 适用多种院校

- 2024-03-0624、25考研公共课免费分享

- 2024-03-05831程序设计语言

- 2024-03-05求资料

2021考研热门话题进入论坛

- 2022-01-24【入版必看】2021考研全程备考规划!

- 2021-12-16424分上岸!21级成都大学广播电视第1名三跨二战上岸经

- 2021-01-20学长学姐帮2020还没对你说的话,今天这就告诉你

- 2024-02-21西南交通大学土木考研

- 2024-01-31华中师范语言所考研资料

- 2024-01-31华中师范大学语言所考研资料

- 2024-01-27武汉大学法学学硕考研经验贴

考研帮地方站更多

你可能会关心:

来考研帮提升效率