3.5 主存储器与CPU的连接

3.5 主存储器与CPU的连接 主存储器用来存放计算机运行期间所需要的程序和数据,它起承上启下的作用,是存储

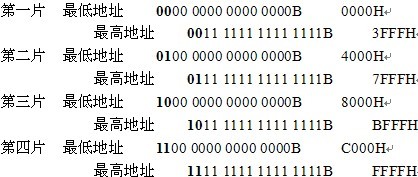

在这种情况下,CPU将提供16根地址线、8根数据线与存储器相连;而存储芯片仅有14根地址线、8根数据线。4个芯片的地址线A13~A0、数据线D7~D0及读写控制信号 都是同名信号并联在一起;CPU的高位地址线

都是同名信号并联在一起;CPU的高位地址线 经过一个地址译码器产生4个片选信号

经过一个地址译码器产生4个片选信号 分别选中4个芯片中的一个。在同一时间内4个芯片中只能有一个芯片被选中。4个芯片的地址分配如下:

分别选中4个芯片中的一个。在同一时间内4个芯片中只能有一个芯片被选中。4个芯片的地址分配如下:

(3)字位同时扩展法。当构成一个容量较大的存储器时,往往需要在字数方向和位数方向上同时扩展,这就是字位同时扩展法,如使用16K×4的存储器芯片,要组成64K×8的存储器,就需要字位同时扩展。

5.片选的方法

如果采用字扩展或字位同时扩展需要用到片选信号,而片选信号的产生可细分为线选法、全译码法和部分译码法。

(1)线选法。线选法就是用除片内寻址外的高位地址线直接(或经反相器)分别接至各个存储芯片的片选端,当某地址线信息为0时,就选中与之对应的存储芯片。这些片选地址线每次寻址时只能有一位有效,不允许同时有多位有效,这样才能保证每次只选中一个芯片(或组)。如果有四片芯片,那么需要四位这样的地址线。线选法的优点是不需要地址译码器,线路简单,选择芯片无须外加逻辑电路,但仅适用于连接存储芯片较少的场合。同时,线选法不能充分利用系统的存储器空间,且把地址空间分成了相互隔离的区域,给编程带来了一定的困难。

(2)全译码法。全译码法将除片内寻址外的全部高位地址线都作为地址译码器的输入,译码器的输出作为各芯片的片选信号,将它们分别接到存储芯片的片选端,以实现对存储芯片的选择。在这种方法中,如果有18位地址线,其中10位用于片内地址编码,那么剩余的8位将全部参加译码,这明显增加了译码电路的难度。全译码法的优点是每片芯片的地址范围是唯一确定的,而且是连续的,也便于扩展,不会产生地址重叠的存储区,但全译码法对译码电路要求较高。

(3)部分译码法。部分译码法用除片内寻址外的高位地址的一部分来译码产生片选信号。如用4片2K×8的存储芯片组成8K×8存储器,需要4个片选信号,因此只需要用两位地址线来译码产生。这种方法综合了前面两种方法的优点,但使用这种方法可能会存在地址重叠区。

6.主存与CPU的连接

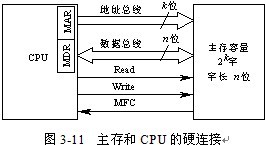

CPU对存储器进行读写操作,首先由地址总线给出地址信号,然后发出读操作或写操作的控制信号,最后在数据总线上进行信息交流。如果将由若干存储芯片构成的存储器和CPU看做两个黑盒子,通过地址总线(AB)、数据总线(DB)、控制总线(CB)相联的结构如图3-11所示。

存储器地址寄存器(MAR)和存储器数据寄存器(MDR)是主存和CPU之间的接口。MAR可以接受来自程序计数器的指令地址或来自地址形成部件的操作数地址,以确定要访问的单元。MDR是向主存写入数据或从主存读出数据的缓冲部件。MAR和MDR从功能上看属于主存,但在小型计算机、微型计算机中常放在CPU内。

CPU与主存的硬连接是两个部件之间联系的物理基础,具体完成读或写还需要两个部件之间的软连接,即CPU向主存发出的读或写命令,这才是两个部件之间有效工作的关键。读写的基本操作如下:

(1)读。读操作是指从CPU送来的地址所指定的存储单元中取出信息,再送给CPU,其操作过程如下:

① 地址→MAR→AB:CPU将地址信号送至地址总线;

② Read:CPU发出读命令;

③ Wait for MFC:等待存储器工作完成信号;

④ M(MAR)→DB→MDR:读出信息经数据总线送至CPU。

(2)写。写操作是指将要写入的信息存入CPU所指定的存储单元中,其操作过程如下:

① 地址→MAR→AB:CPU将地址信号送至地址总线;

② 数据→MDR→DB:CPU将要写入的数据送至数据总线;

③ Write:CPU发出写命令;

④ Wait for MFC:等待存储器工作完成信号。

由于CPU和主存的速度存在着差距,所以两者之间的速度匹配是很关键的。通常有两种匹配方式:同步存储器读取和异步存储器读取。上面给出的读写基本操作是以异步存储器读取来考虑的,CPU和主存之间没有统一的时钟,由主存工作完成信号(MFC)通知CPU“主存工作已完成”。

希赛教育研究生院专家提示:对于同步存储器读取,CPU和主存采用统一时钟,同步工作,因为主存速度较慢,所以CPU与之配合必须放慢速度。在这种方式中,不需要主存工作完成信号。

关于"最后阶段,真题的正确打开方式_备考经验_考研帮"有15名研友在考研帮APP发表了观点

扫我下载考研帮

最新资料下载

- 2024-03-15考研资料免费分享,公共课专业课都有,23最新的

- 2024-03-1125考研公共课免费分享

- 2024-03-06mpa复试

- 2024-03-0624新传考研资料 适用多种院校

- 2024-03-0624、25考研公共课免费分享

- 2024-03-05831程序设计语言

- 2024-03-05求资料

2021考研热门话题进入论坛

- 2022-01-24【入版必看】2021考研全程备考规划!

- 2021-12-16424分上岸!21级成都大学广播电视第1名三跨二战上岸经

- 2021-01-20学长学姐帮2020还没对你说的话,今天这就告诉你

- 2024-02-21西南交通大学土木考研

- 2024-01-31华中师范语言所考研资料

- 2024-01-31华中师范大学语言所考研资料

- 2024-01-27武汉大学法学学硕考研经验贴

考研帮地方站更多

你可能会关心:

来考研帮提升效率