3.3 半导体随机存取存储器

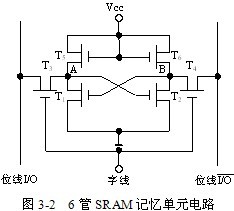

3.3 半导体随机存取存储器 半导体随机存储器RAM又可分为SRAM和DRAM两种,本节分别介绍这两种半导体存取存

3.3.2 DRAM存储器的工作原理

DRAM存储器是通过电容存储电荷的原理来寄存信息的。电容上有足够多的电荷表示存1,电容上无电荷表示存0。电容上的电荷一般只能维持1~2ms。再生或刷新时,必须在2ms内对其所有存储单元恢复一次原状态。与SRAM相比,集成度更高、功耗更低。

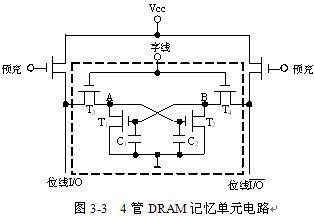

1.DRAM的记忆单元

如果6管SRAM记忆单元电路中的两个负载管(T5和T6)去掉,便形成4管DRAM记忆单元电路,如图3-3所示。负载回路断开后,保持状态时没有外加电源供电,因而T1和T2管不再构成双稳态触发器,所以DRAM记忆单元是靠电路中的栅极电容C1和C2来存储信息的。

图3-3中虚线框外的两个MOS管是公用的预充管,不算在记忆单元电路中。

由于MOS管栅极的输入电阻很大,所以栅极泄漏电流很小,即使没有负载管的供电,栅极电容上的电荷也能保存相当一段时间。然而,栅极电容上的电荷数目毕竟是有限的,虽然泄放速度很慢,但经过一段时间后仍然会使记忆单元中存储的信息丢失,因此每隔一定的时间必须向栅极电容补充一次电荷,这个过程称为刷新。

DRAM集成度高,功耗小,但存取速度慢,一般用来组成大容量主存系统。

进一步减少记忆单元中MOS管的数目可形成更简单的3管DRAM记忆单元或单管DRAM记忆单元。显然,单管DRAM记忆单元与4管DRAM记忆单元比较,具有功耗更小、集成度更高的优点。

2.DRAM的刷新间隔

前面已经提到,为了维持DRAM记忆单元的存储信息,每隔一定时间必须刷新。那么每隔多少时间进行一次刷新操作呢?这主要是根据栅极电容上电荷的泄放速度来决定的。一般选定的最大刷新间隔为2ms或4ms甚至更大,也就是说,应在规定的时间内,将全部存储体刷新一遍。

说到刷新,还要提到另一个概念,那就是重写(再生)。刷新和重写是两个完全不同的概念,切不可加以混淆。重写是随机的,某个存储单元只有在破坏性读出之后才需要重写。而刷新是定时的,即使许多记忆单元长期未被访问,若不及时补充电荷的话,信息也会丢失。重写一般是按存储单元进行的,而刷新通常是以存储体矩阵中的一行为单位进行的。

3.DRAM的刷新方式

常见的刷新方式有集中式、分散式和异步式3种。

(1)集中刷新方式。在允许的最大刷新间隔(如2ms)内,按照存储芯片容量的大小集中安排若干个刷新周期,刷新时停止读写操作。

刷新时间=存储矩阵行数×刷新周期

这里的刷新周期是指刷新一行所需要的时间,由于刷新过程就是“假读”的过程,所以刷新周期就等于存取周期。例如,对具有1024个记忆单元(排列成32×32的存储矩阵)的存储芯片进行刷新,刷新是按行进行的,且每刷新一行占用一个存取周期,所以共需32个周期以完成全部记忆单元的刷新。假设存取周期为500ns(0.5μs),则在2ms内共可以安排4000个存取周期,从0~3967个周期内进行读写操作或保持,而从3968~3999最后32个周期集中安排刷新操作,如图3-4所示。

集中刷新方式的优点是读写操作时不受刷新工作的影响,因此系统的存取速度比较快。主要缺点是在集中刷新期间必须停止读写,这一段时间称为“死区”,而且存储容量越大,死区就越长。

(2)分散刷新方式。分散刷新是指将刷新操作分散到每个存取周期内进行,此时系统的存取周期被分为两个部分,前一部分时间进行读写操作或保持,后一部分时间进行刷新操作。在一个系统存取周期内刷新存储矩阵中的一行。

这种刷新方式增加了系统的存取周期,如存储芯片的存取周期为0.5μs,则系统的存取周期应为1μs。仍以前述的32×32矩阵为例,整个存储芯片刷新一遍需要32μs,如图3-5所示。

从图3-5中可以看出,这种刷新方式没有死区,但是,它也有很明显的缺点,一是加长了系统的存取周期,降低了整机的速度;二是刷新过于频繁(本例中每32μs就重复刷新一遍),尤其是当存储容量比较小的情况下,没有充分利用所允许的最大刷新间隔(2ms)。

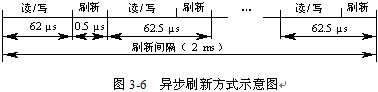

(3)异步刷新方式。这种刷新方式可以看成是集中刷新和分散刷新两种方式的结合,它充分利用了最大刷新间隔时间,把刷新操作平均分配到整个最大刷新间隔时间内进行,故有:

相邻两行的刷新间隔 = 最大刷新间隔时间/行数

对于32×32矩阵,在2ms内需要将32行刷新一遍,所以相邻两行的刷新时间间隔=2ms/32=62.5μs,即每隔62.5s安排一个刷新周期。在刷新时封锁读写,如图3-6所示。

异步刷新方式虽然也有死区,但比集中刷新方式的死区小得多,仅为0.5μs。这样可以避免使CPU连续等待过长的时间,而且减少了刷新次数,是比较实用的一种刷新方式。

消除死区的方法,还可采用不定期的刷新方式。其基本做法是:把刷新操作安排在CPU不访问存储器的空闲时间里,如利用CPU取出指令后进行译码的这段时间,这时,刷新操作对CPU是透明的,故又称透明刷新。这种方式既不会出现死区,又不会降低存储器的存取速度;但是控制比较复杂,实现起来比较困难。

4.刷新控制

为了控制刷新,往往需要增加刷新控制电路。刷新控制电路的主要任务是解决刷新和CPU访问存储器之间的矛盾。通常,当刷新请求和访存请求同时发生时,应优先进行刷新操作。也有些DRAM芯片本身具有自动刷新功能,即刷新控制电路在芯片内部。

DRAM的刷新要注意以下问题:

(1)无论是由外部刷新控制电路产生刷新地址逐行循环地刷新,还是芯片内部的刷新地址计数器自动地控制刷新,都不依赖于外部的访问,刷新对CPU是透明的;

(2)刷新通常是一行一行地进行的,每一行中各记忆单元同时被刷新,故刷新操作时仅需要行地址,不需要列地址;

(3)刷新操作类似于读出操作,但又有所不同。因为刷新操作仅是给栅极电容补充电荷,不需要信息输出。另外,刷新时不需要加片选信号,即整个存储器中的所有芯片同时被刷新;

(4)因为所有芯片同时被刷新,所以在考虑刷新问题时,应当从单个芯片的存储容量着手,而不是从整个存储器的容量着手。

关于"最后阶段,真题的正确打开方式_备考经验_考研帮"有15名研友在考研帮APP发表了观点

扫我下载考研帮

最新资料下载

- 2024-03-15考研资料免费分享,公共课专业课都有,23最新的

- 2024-03-1125考研公共课免费分享

- 2024-03-06mpa复试

- 2024-03-0624新传考研资料 适用多种院校

- 2024-03-0624、25考研公共课免费分享

- 2024-03-05831程序设计语言

- 2024-03-05求资料

2021考研热门话题进入论坛

- 2022-01-24【入版必看】2021考研全程备考规划!

- 2021-12-16424分上岸!21级成都大学广播电视第1名三跨二战上岸经

- 2021-01-20学长学姐帮2020还没对你说的话,今天这就告诉你

- 2024-02-21西南交通大学土木考研

- 2024-01-31华中师范语言所考研资料

- 2024-01-31华中师范大学语言所考研资料

- 2024-01-27武汉大学法学学硕考研经验贴

考研帮地方站更多

你可能会关心:

来考研帮提升效率